Answer the question

In order to leave comments, you need to log in

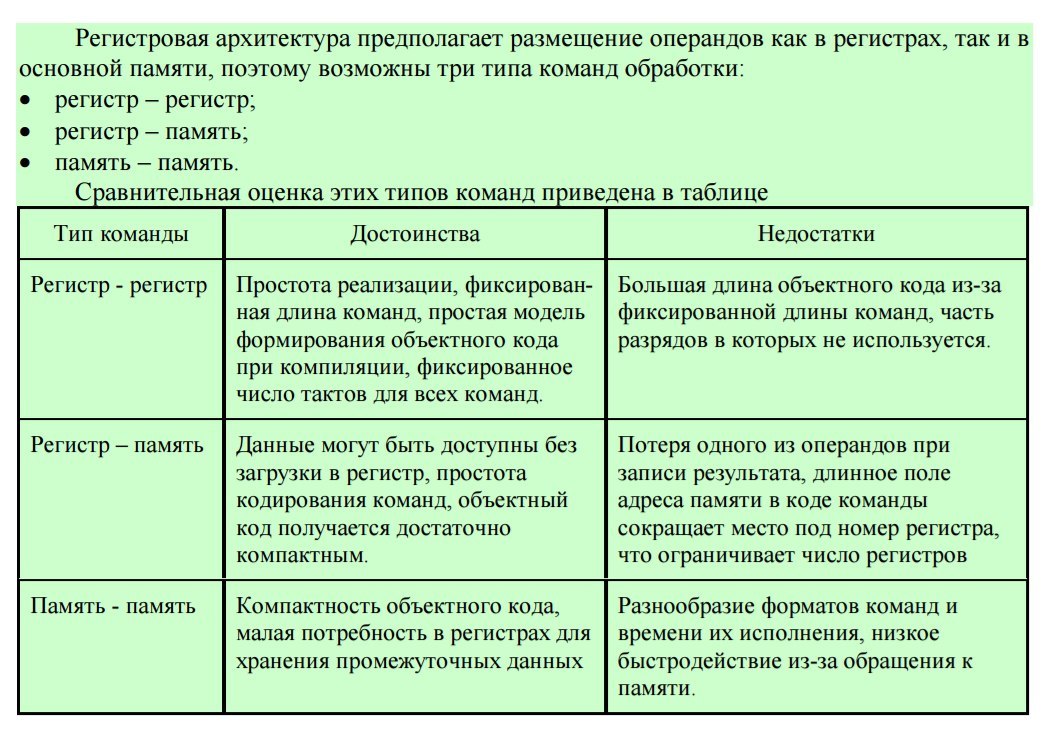

Why can there be more than three types of processor processing instructions?

My teacher claims that this text contains inaccuracies and errors, in particular:

1. The register architecture involves the placement of operands not only in registers and main memory, therefore, there must be more than three types of processing instructions.

2. In the column of the table "Disadvantages" there are statements that are inaccurate, and under some additional conditions - erroneous.

Please help me understand what exactly is meant here in the first and second cases?

Answer the question

In order to leave comments, you need to log in

The cache is not in the table.

The second disadvantage would be valid for memory addressing, which is not covered by the register format (8 bits and 1 megabyte). And in general, today there are command schedulers that monitor commands and put them on the necessary branches of the processor and external devices, taking into account differences in formats and execution speed (direct memory access, a vivid example).

Just an outdated sign, you need to look for another one.

On the first point - he probably hints at the input / output ports.

But it generally depends on the processor - there are those that support ports and they have special instructions for them, and there are places where it is necessary to decrypt at memory addresses (but there are nuances of execution).

On the second, briefly - commands are not fixed length (for example, with prefixes); three operand commands (like arm ADD R0, R1, R2; R0 = R1 + R2); prefetch cache pipeline speculative load, etc.

Didn't find what you were looking for?

Ask your questionAsk a Question

731 491 924 answers to any question