Answer the question

In order to leave comments, you need to log in

How does 4x3 bit memory work?

Good afternoon!

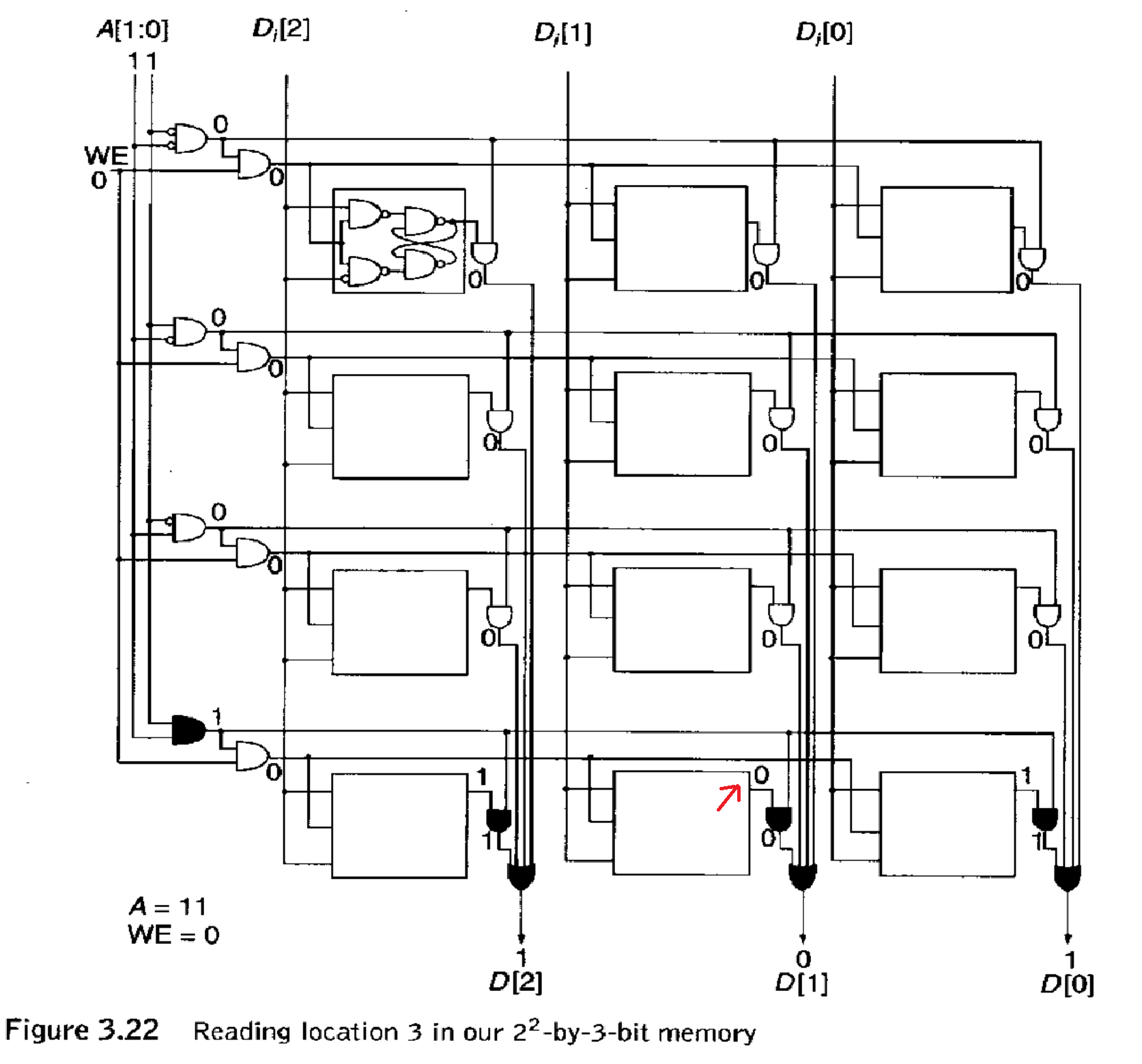

I ask for help, there were difficulties with understanding the 4x3 bit memory scheme, namely:

There are actually two questions:

1. What are the values of Di[2], Di[1], Di[0] ? (this is not mentioned in the text). It is here that these values \u200b\u200bare not affected by anything, because WE=0, so the AND outputs for any values of Di will be 0. Just wondering if they equal something, or if not set, then by default 0?

2. How exactly these values are obtained at the outputs D[2], D[1], D[0] ? Why D[1]=0 ? I understand how the D trigger works, but I don’t understand how the output 0 is obtained in this case (which output I marked with a red arrow)?

Thanks in advance for your reply!

Original text:

"Figure 3.22 shows the process of reading location 3. The code for 3 is 11. The addres s A[1:0] = 11 is decoded, and the bottom word line is asserted. Note that the three other decoder outputs are not asserted . That is, they have the value 0. The value stored in location 3 is 101. These three bits are each ANDed with their word line producing the bits 101, which are supplied to the three output OR gates. the OR gates are 0, since they have been produced by ANDing with unasserted word lines. The result is that D[2:0] = 101. That is, the value stored in location 3 is output by the OR gates. Memory can be written in a similar fashion.The address specified by A[1:0] is presented to the address decoder, resulting in the correct word line being asserted.With WE asserted as well,the three bits Di[2:0] can be written into three gated latches corresponding to that word line."

Answer the question

In order to leave comments, you need to log in

What are the values of Di[2], Di[1], Di[0]? (this is not mentioned in the text)

Didn't find what you were looking for?

Ask your questionAsk a Question

731 491 924 answers to any question